2022年超大规模集成电路可测性设计(DFT)技术与实践 赋能先进芯片设计

随着半导体工艺持续演进至纳米甚至更先进节点,超大规模集成电路(VLSI)的复杂度呈指数级增长,晶体管数量动辄达到数十亿乃至数百亿。在此背景下,芯片的可测性(Testability)已不再是设计流程的后期附加环节,而是贯穿始终的核心设计约束与关键质量指标。2022年,可测性设计(Design for Testability, DFT)技术持续演进,其理论与实践紧密围绕提升测试质量、控制测试成本与缩短上市周期三大目标展开,为复杂芯片的成功量产与可靠应用提供了坚实保障。

一、DFT的核心挑战与技术演进方向

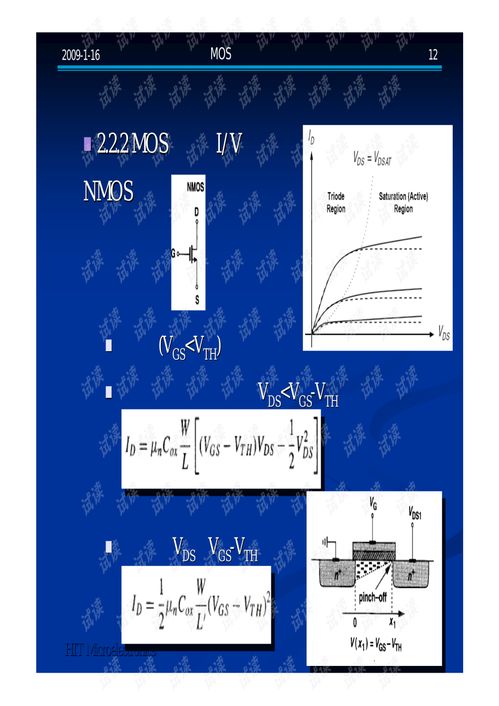

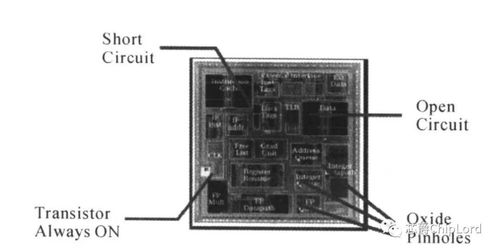

在先进工艺节点,DFT面临多重挑战:首先是测试数据量(Test Data Volume)与测试应用时间(Test Application Time)的爆炸式增长,直接推高了测试成本;其次是物理缺陷模型日趋复杂,传统的固定型故障(Stuck-at Fault)模型已不足以覆盖全部缺陷,需要引入如转换时延故障、小延迟缺陷、桥接故障等更精细的模型;低功耗设计、多电压域、复杂时钟网络以及三维集成等技术引入的测试访问与隔离难题。

针对这些挑战,2022年的DFT技术与实践呈现出以下关键趋势:

- 扫描测试(Scan Test)的智能化与压缩技术深化:自适应扫描压缩、基于AI的测试模式生成与优化,在保证高故障覆盖率的显著压缩测试向量集。

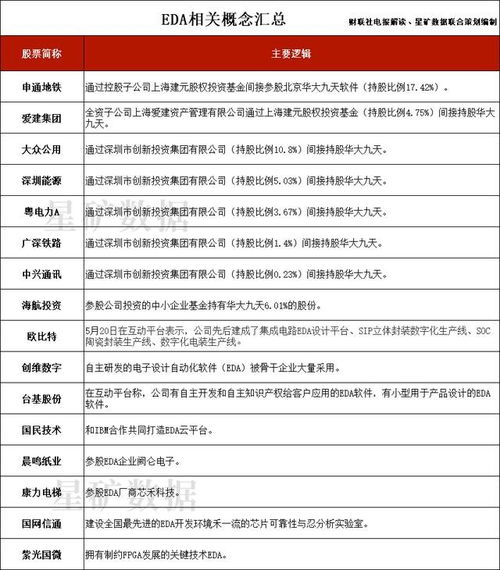

- 内建自测试(BIST)的广泛应用与升级:特别是逻辑内建自测试(LBIST)和内存内建自测试(MBIST),不仅用于片上存储器和逻辑核,更向模拟/混合信号电路、高速接口(如SerDes)和人工智能加速器扩展。

- 面向系统级测试与硅后验证:DFT架构开始更多考虑芯片在系统板级乃至最终产品中的测试需求,支持系统级测试(SLT)访问与调试。利用DFT基础设施进行硅后性能监控、老化监测与现场诊断。

- 与设计流程的早期集成:DFT规划与实现已大幅提前至架构设计与RTL编码阶段,通过UPF(统一功耗格式)实现多电压域测试,并利用形式验证工具确保DFT逻辑的功能正确性。

二、关键技术实践与行业应用

在实践中,现代DFT流程通常包含以下核心步骤与技术的综合应用:

- 层次化DFT与测试访问机制(TAM):对于包含多个IP核的SoC,采用层次化DFT策略,通过标准接口(如IEEE 1500)封装每个IP的测试逻辑,并利用片上网络(NoC)或专用TAM高效调度测试数据,实现并行测试,缩短整体测试时间。

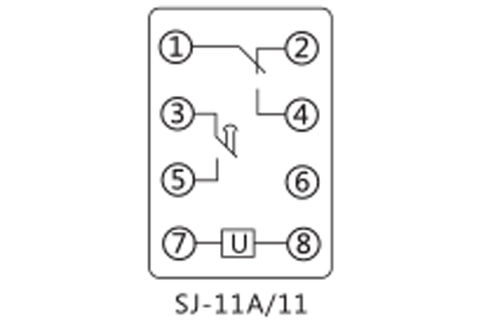

- 基于JTAG/IEEE 1149.1/1687(IJTAG)的灵活访问与控制:JTAG边界扫描用于板级互联测试,而更先进的IJTAG网络则成为访问和控制片内各类DFT结构(扫描链、BIST控制器、传感器等)的“神经中枢”,极大增强了测试的可控性与可观测性。

- 功耗感知测试:在测试模式下,大规模电路同时翻转会引发远超功能模式的峰值功耗,可能导致电压下降、热量积聚甚至芯片损坏。因此,采用测试向量排序、时钟门控、片上解压缩器低功耗设计等技术,实施严格的测试功耗管理已成为必需。

- 良率学习与诊断驱动良率提升(DDYA):利用DFT产生的失效日志,结合先进诊断软件,可以精确定位到物理缺陷的位置和类型,反馈至制造厂进行工艺调优,形成“测试-诊断-修复”的闭环,加速良率爬升。

三、未来展望

DFT技术将继续与人工智能、云计算深度融合。AI将更深度地应用于测试生成优化、故障诊断预测和自适应测试调度。云平台则为海量测试数据的存储、分析与协作提供了可能。面对Chiplet(芯粒)和3D IC等异构集成技术,DFT需要发展出跨Die、跨堆叠层的协同测试策略与标准,确保封装后系统的整体可测试性。

总而言之,在2022年及可预见的DFT已从一项“保险”技术,演变为确保超大规模集成电路设计成功、制造经济性与产品可靠性的战略性赋能技术。它要求设计工程师、测试工程师和制造工程师紧密协作,在追求性能、功耗、面积(PPA)极致的将“可测性”基因深刻植入芯片设计的每一个阶段。

如若转载,请注明出处:http://www.mytouchtime.com/product/74.html

更新时间:2026-04-30 22:51:48