超大规模集成电路设计中的MOS器件原理与应用(三)

在超大规模集成电路(VLSI)设计中,金属-氧化物-半导体(MOS)器件构成了现代芯片的基石。本部分将深入探讨MOS器件在集成电路设计中的核心原理、关键特性及其在电路层面的应用。

一、MOS器件的基本结构与工作原理

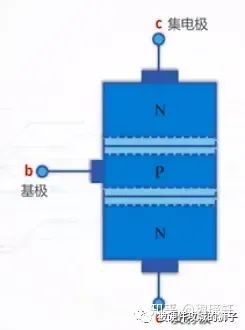

MOS器件,特别是MOSFET(金属-氧化物-半导体场效应晶体管),其基本结构由源极、漏极、栅极和衬底(体端)构成。栅极通过一层极薄的绝缘氧化物(如SiO₂)与半导体沟道隔离,形成电容结构。当栅极施加电压时,会在半导体表面感应出电荷,从而控制源漏之间的电流通路。这一电压控制电流的特性,使其成为理想的开关和放大元件。

工作原理基于场效应:栅压变化改变沟道区的载流子浓度和类型(电子或空穴),进而调制沟道电导。NMOS依靠电子导电,PMOS依靠空穴导电,两者互补构成CMOS技术,实现了极低的静态功耗,成为VLSI的主流。

二、MOS器件的关键电学特性与模型

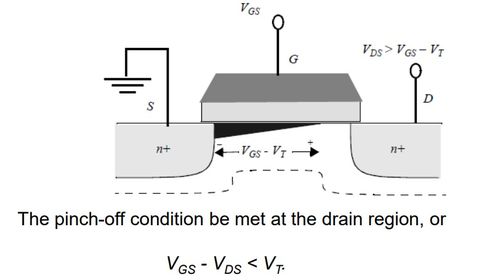

- 电流-电压(I-V)特性:包括线性区和饱和区。在VGS > Vth(阈值电压)且VDS较小时,器件工作在线性区,电流随VDS近似线性变化;当VDS增大至VDS > VGS - Vth时,进入饱和区,电流基本保持恒定,对电压变化不敏感,这一特性对模拟电路的增益和数字电路的噪声容限至关重要。

- 阈值电压(Vth):是器件开启的关键参数,受掺杂浓度、氧化物厚度、栅极材料及体效应(背栅偏置)影响。在深亚微米及以下工艺中,短沟道效应会导致Vth下降,成为设计挑战。

- 寄生参数:包括栅源/栅漏覆盖电容、结电容以及串联电阻等。这些寄生效应在高频或高速电路中会显著影响速度、功耗和信号完整性,必须在电路设计中精确建模和优化。

- 工艺角与变异:制造过程中的工艺波动会导致器件参数(如长度、宽度、氧化物厚度、掺杂)发生变化,从而影响性能。设计时必须考虑快、慢、典型等多种工艺角,并通过仿真确保电路在所有条件下均能可靠工作。

三、MOS器件在集成电路设计中的应用

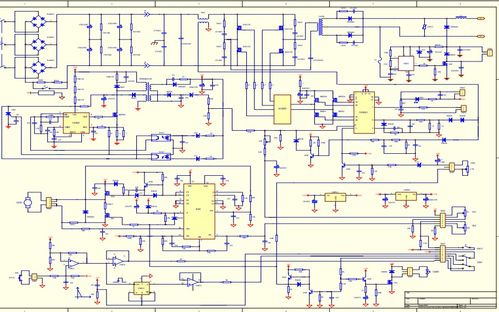

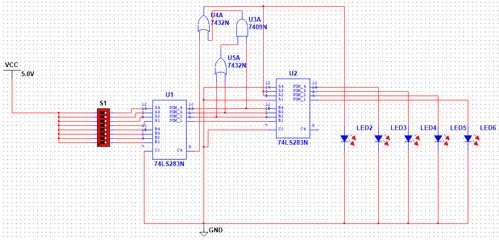

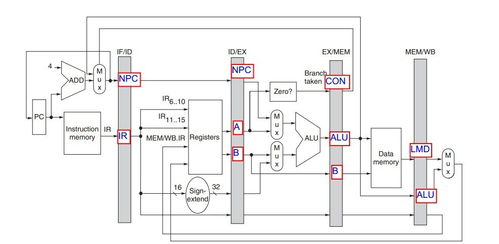

- 数字电路设计:MOSFET是构成反相器、与非门、或非门等基本逻辑门的核心。CMOS技术通过将NMOS和PMOS配对,实现了在稳态下几乎零静态功耗的逻辑功能。在VLSI中,数百万至数十亿个这样的晶体管被集成,通过版图设计实现复杂的逻辑功能、存储单元(如SRAM的6T单元)和时序电路(触发器、锁存器)。

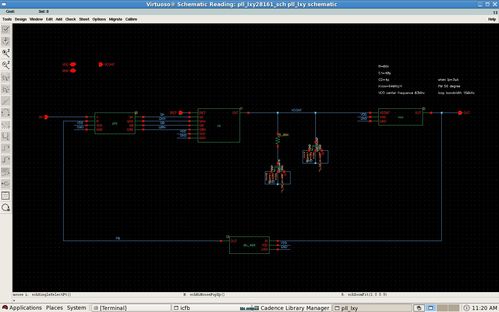

- 模拟与混合信号电路设计:MOS器件用作放大器、电流镜、差分对、开关等。其跨导(gm)、输出电阻(ro)等小信号参数直接决定了放大器的增益、带宽和线性度。在数据转换器(ADC/DAC)、锁相环(PLL)、电源管理电路中,MOS器件的匹配性、噪声特性(热噪声、闪烁噪声)和开关特性是关键设计考量。

- 存储器设计:动态随机存取存储器(DRAM)利用MOS晶体管作为存取开关,控制电容的充放电;闪存(Flash)则利用浮栅MOS器件存储电荷以实现非易失性。器件尺寸的微缩和可靠性的提升直接推动了存储器容量和性能的进步。

- 低功耗与高性能设计:随着工艺节点进入纳米尺度,功耗(特别是静态漏电流功耗)和性能的权衡成为核心。技术如多阈值电压(Multi-Vt)、电源关断(Power Gating)、体偏置(Body Biasing)以及新型器件结构(如FinFET、GAA)被广泛应用,以在保持性能的同时有效控制功耗。

四、设计挑战与未来趋势

当前,MOS器件设计面临短沟道效应、量子隧穿、热载流子效应、工艺变异加剧以及互连线延迟主导等严峻挑战。为了延续摩尔定律,业界正在探索:

- 新器件结构:如全环绕栅极(GAA)纳米片晶体管,提供更好的栅极控制能力。

- 新材料:High-k栅介质替代SiO₂,金属栅替代多晶硅,以及沟道材料(如应变硅、III-V族化合物)的引入。

- 新集成范式:三维集成(3D IC)、芯粒(Chiplet)技术,从系统层面提升性能和能效。

深入理解MOS器件原理是成功进行超大规模集成电路设计的先决条件。设计师必须在器件物理、工艺技术和电路架构之间取得精妙平衡,才能创造出功能强大、能效卓越的芯片,持续推动信息技术的革命。

如若转载,请注明出处:http://www.mytouchtime.com/product/62.html

更新时间:2026-04-14 12:20:37