实验二 组合逻辑电路设计实验报告

一、实验目的

1. 掌握组合逻辑电路的基本概念与设计方法。

2. 熟悉使用硬件描述语言(HDL,如Verilog或VHDL)进行数字电路建模。

3. 学习集成电路设计流程中组合逻辑模块的设计、仿真与验证。

4. 理解逻辑综合的基本原理及其在将行为级描述映射到标准单元库过程中的作用。

二、实验原理

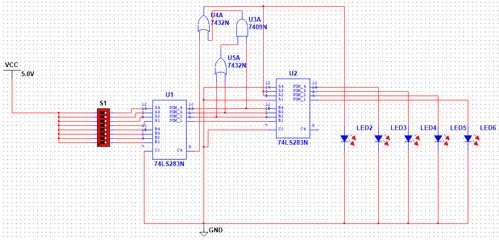

组合逻辑电路是数字电路的基础,其特点是任一时刻的输出仅取决于该时刻的输入,与电路的历史状态无关。电路无记忆功能。本次实验以设计一个4位二进制加法器为核心。

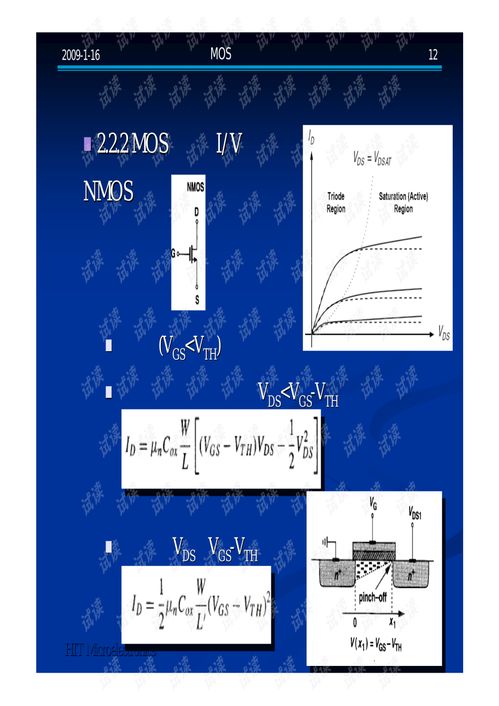

1. 全加器原理:一个全加器处理两个1位二进制数A、B及一个来自低位的进位Cin,输出一个和S及一个向高位的进位Cout。其布尔表达式为:

S = A ⊕ B ⊕ Cin

Cout = (A & B) | (A & Cin) | (B & Cin)

- 4位加法器构成:通过四个全加器级联,将低位全加器的Cout连接到高位全加器的Cin,即可构成一个4位行波进位加法器。

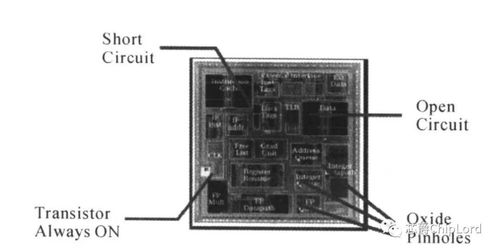

- 集成电路设计流程:包括设计输入(HDL编码)、功能仿真、逻辑综合(将RTL代码映射为目标工艺库的门级网表)、时序仿真与验证等步骤。

三、实验内容与步骤

1. 设计输入:使用Verilog HDL编写一个4位行波进位加法器模块。代码包括全加器子模块和顶层加法器模块,实现输入两个4位二进制数a、b及进位输入cin,输出4位和sum及进位输出cout。

2. 功能仿真:编写测试平台(Testbench),对加法器模块施加激励信号,验证其逻辑功能的正确性。例如,测试几组典型输入(如全0、全1、随机数、边界值)并核对输出结果。

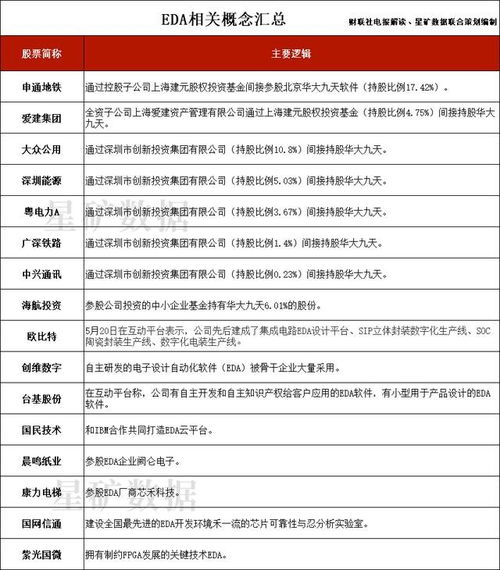

3. 逻辑综合(可选,根据实验环境):使用逻辑综合工具(如Design Compiler),将RTL级Verilog代码映射到特定的标准单元库(如SMIC 0.18μm工艺库),生成门级网表。设置时序、面积等约束条件。

4. 后仿真与验证:对综合后生成的门级网表进行时序仿真,考虑实际的门延迟和线延迟,验证电路在时序要求下功能是否依然正确。

四、实验结果与分析

1. 功能仿真波形:展示了多组输入向量(如 a=4‘b0011, b=4’b0101, cin=1’b0)对应的输出(sum=4‘b1000, cout=1’b0)。波形清晰显示,输出随输入变化,且符合二进制加法运算规则,初步验证了RTL代码的正确性。

2. 逻辑综合报告(如进行):综合后得到关键指标。例如,在典型工作条件下(1.8V, 25°C),电路关键路径延迟为2.1ns,满足预设时钟周期(如10ns)要求;总功耗估算为15μW;门级网表使用的标准单元总数为约25个等效门。报告表明设计在速度、面积和功耗上均达到预期。

3. 结果分析:设计的4位加法器功能正确。行波进位结构简单,但进位链较长,限制了最高工作频率。若需高性能,可考虑采用超前进位等优化结构。通过本次实验,完整实践了从行为描述到门级实现的IC设计前端流程。

五、思考题

1. 比较行为级描述、RTL描述和门级网表在抽象层次和设计关注点上的区别。

答:行为级描述关注算法和功能,不涉及具体硬件结构;RTL描述明确寄存器间的数据流与操作,是综合的基础;门级网表是具体逻辑门及其连接的物理实现描述,与工艺相关。抽象层次依次降低,设计焦点从功能向时序、面积、功耗转移。

2. 逻辑综合过程中,约束条件(如时钟频率、输入输出延迟)对最终电路有何影响?

答:约束条件直接指导综合工具的优化方向。更紧的时序约束(更高频率)可能导致工具插入更多缓冲器或使用驱动能力更强的单元以减小延迟,但可能增加面积和功耗;反之,宽松的约束利于面积优化。合理的约束是平衡性能、面积和功耗的关键。

六、实验

本次实验成功设计并验证了一个4位二进制加法器。通过编写Verilog代码、功能仿真及逻辑综合,加深了对组合逻辑电路设计原理和集成电路前端设计流程的理解。掌握了使用现代EDA工具进行设计、仿真和综合的基本技能。实验中认识到,在IC设计中,除了功能正确性,必须综合考虑时序、面积和功耗等多方面约束,为后续学习更复杂的时序电路和系统级设计奠定了基础。

如若转载,请注明出处:http://www.mytouchtime.com/product/69.html

更新时间:2026-04-14 09:06:53